# **Revision History**

| Version | Content      | Date     | Page |

|---------|--------------|----------|------|

| 1.0     | New creation | 2024/3/1 | All  |

|         |              |          |      |

|         |              |          |      |

|         |              |          |      |

|         |              |          |      |

|         |              |          |      |

|         |              |          |      |

|         | shore oweson |          |      |

1

## Contents

| 1. | OVERVIEW                                           | 3  |

|----|----------------------------------------------------|----|

| 2. | FEATURES                                           | 4  |

| 3. | MECHANICAL SPECIFICATION                           | 5  |

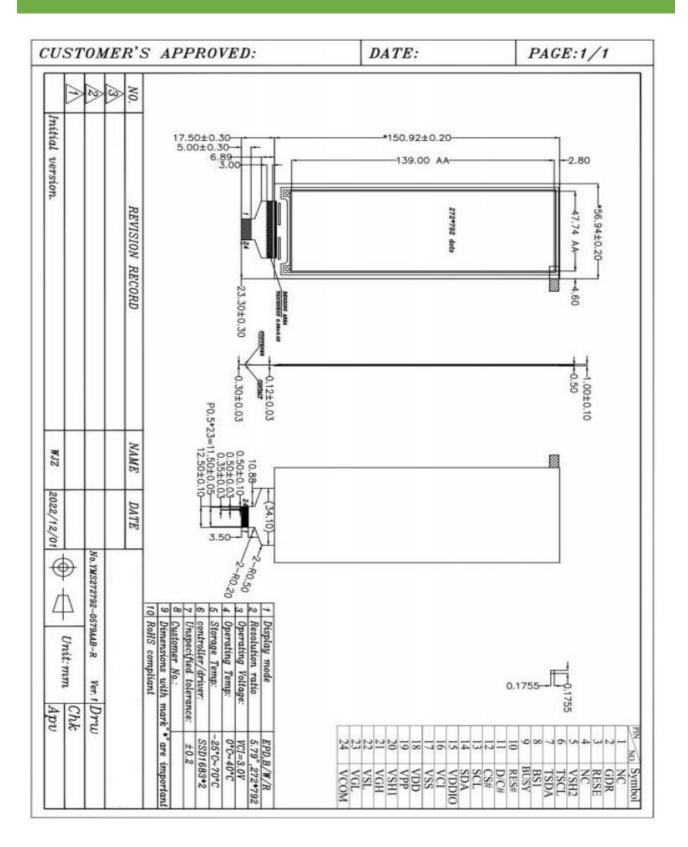

| 4. | MECHANICAL DRAWING OF EPD MODULE                   | 6  |

| 5. | INPUT/OUTPUT PIN ASSIGNMENT                        | 7  |

| 6. | ELECTRICAL CHARACTERISTICS                         | 9  |

|    | 6.1 Absolute Maximum Rating                        | 9  |

|    | 6.2 DC Characteristics                             |    |

|    | 6.3 AC Characteristics                             |    |

|    | 6.3.1 MCU Interface Selection                      | 11 |

|    | 6.3.2 MCU Serial Interface (4-wire SPI)            | 11 |

|    | 6.3.3 MCU Serial Peripheral Interface (3-wire SPI) | 12 |

|    | 6.4.4 Interface Timing                             | 14 |

| 7. | COMMAND TABLE                                      | 15 |

| 8. | OPTICAL SPECIFICATIONS                             | 29 |

| 9. | HANDLING, SAFETY, AND ENVIRONMENT REQUIREMENTS     | 30 |

|    | ). RELIABILITY TEST                                |    |

|    | . REFERNCE CIRCUIT                                 |    |

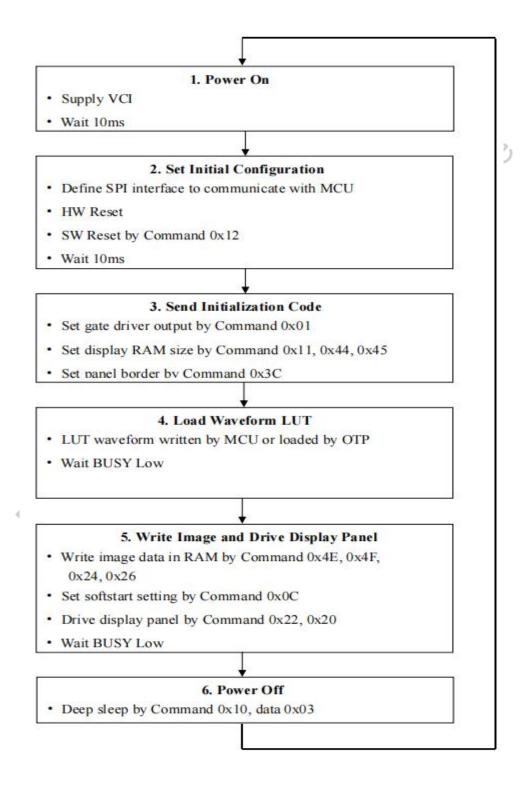

| 12 | . TYPICAL OPERATING SEQUENCE                       | 33 |

|    | 12.1 Normal Operation Flow                         | 33 |

|    | 12.2 Normal Operation Reference Program            |    |

| 13 | . INSPECTION METHOD AND CONDITION                  |    |

|    | 13.1 Inspection Condition                          |    |

|    | 13.2 Zone Definition                               | 35 |

|    | 13.3 General Inspection Standards for Products     | 36 |

|    | 13.3.1 Appearance Inspection Standard              |    |

| 14 | PACKAGING                                          | 39 |

|    |                                                    |    |

SV

## 1. OVERVIEW

5.79 inch e-Paper (B) is an Active Matrix Electrophoretic Display (AM EPD), with interface and a reference system design. The display is capable to display images at 1-bit white, black and red full display capabilities. The 5.79 inch active area contains 272×792 pixels. The module is a TFT-array driving electrophoresis display, with integrated circuits including gate driver, source driver, MCU interface, timing controller, oscillator, DC-DC, SRAM, LUT, VCOM. Module can be used in portable electronic devices, such as Electronic Shelf Label (ESL) System.

nore owesome

hordwore

#### **FEATURES** 2.

- 272×792 pixels display ∻

- High contrast High reflectance ∻

- ♦ Ultra wide viewing angle Ultra low power consumption

- ♦ Pure reflective mode

- $\diamond$  Bi-stable display

- Commercial temperature range ∻

- ♦ Landscape portrait modes

- Hard-coat antiglare display surface ∻

- Ultra Low current deep sleep mode ∻

- On-chip display RAM ∻

- no  $\diamond$  Waveform can stored in On-chip OTP or written by MCU

- ♦ Serial peripheral interface available

- ♦ On-chip oscillator

- ♦ On-chip booster and regulator control for generating VCOM, Gate and Source driving voltage

- I<sup>2</sup>C signal master interface to read external temperature sensor ∻

- ∻ Support partial update mode

- Built-in temperature sensor ∻

## 3. MECHANICAL SPECIFICATION

| Parameter           | Specification                  | Unit            | Remark  |

|---------------------|--------------------------------|-----------------|---------|

| Screen Size         | 5.79                           | Inch            |         |

| Display Resolution  | 272(H) x 792(V)                | Pixel           | DPI:144 |

| Active Area         | 47.74 x 139.00                 | mm              |         |

| Pixel Pitch         | 0.1755 x 0.1755                | mm              |         |

| Pixel Configuration | Rectangle                      |                 |         |

| Outline Dimension   | 56.94 (H) × 150.92(V) × 1.0(D) | mm              |         |

| Weight              | 15.7±0.5                       | g               |         |

|                     | shore owesome he               | 10 <sup>1</sup> |         |

5

## 4. MECHANICAL DRAWING OF EPD MODULE

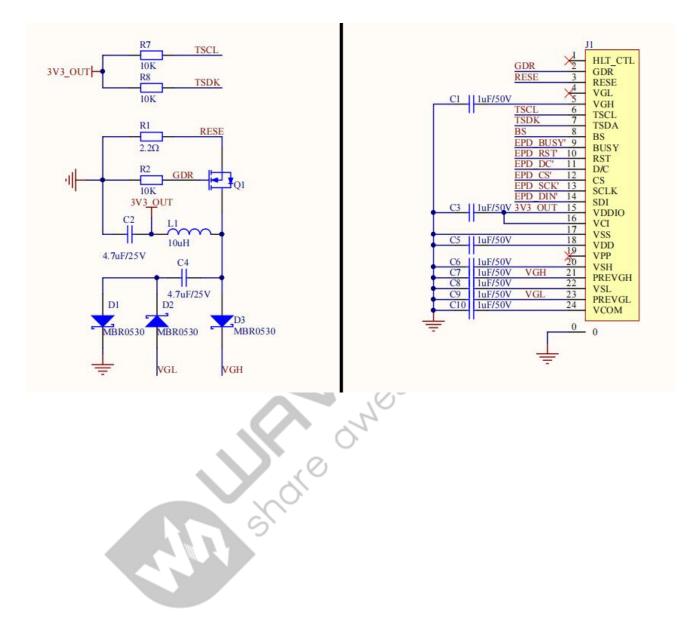

## 5. INPUT/OUTPUT PIN ASSIGNMENT

| NO. | Name  | I/O | Description                                                                                                                                             | Remark    |

|-----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1   | NC    |     | Do not connect with other NPC pins                                                                                                                      | Keep Open |

| 2   | GDR   | 0   | N-Channel MOSFET Gate Drive Control                                                                                                                     |           |

| 3   | RESE  | I   | Current Sense Input for the Control Loop                                                                                                                |           |

| 4   | NC    |     | Do not connect with other NC pins                                                                                                                       | Keep Open |

| 5   | VSH2  | С   | Positive Source driving voltage(Red)                                                                                                                    |           |

| 6   | TSCL  | 0   | I2C Interface to digital temperature sensor Clock pin<br>External pull up resistor is required when connecting to I2C<br>slave.<br>When not in use: VSS |           |

| 7   | TSDA  | I/O | I2C Interface to digital temperature sensor Data pin<br>External pull up resistor is required when connecting to I2C<br>slave.<br>When not in use: VSS  |           |

| 8   | BS1   | I   | Bus Interface selection pin                                                                                                                             | Note 5-5  |

| 9   | BUSY  | 0   | Busy state output pin                                                                                                                                   | Note 5-4  |

| 10  | RES#  | I   | Reset signal input, Active Low                                                                                                                          | Note 5-3  |

| 11  | D/C#  | I   | Data/Command control pin                                                                                                                                | Note 5-2  |

| 12  | CS#   | I   | Chip select input pin                                                                                                                                   | Note 5-1  |

| 13  | SCL   | I   | Serial Clock pin (SPI)                                                                                                                                  |           |

| 14  | SDA   | I/O | Serial Data pin (SPI)                                                                                                                                   |           |

| 15  | VDDIO | Р   | Power supply for interface logic pins.<br>It should be connected with VCI.                                                                              |           |

| 16  | VCI   | Р   | Power supply for the chip                                                                                                                               |           |

| 17  | VSS   | Р   | Ground                                                                                                                                                  |           |

| 18  | VDD   | с   | Core logic power pin VDD can be regulated internally from VCI. A capacitor should be connected between VDD and VSS.                                     |           |

| 19  | VPP   | Р   | FOR TEST                                                                                                                                                |           |

| 20  | VSH1  | С   | Positive Source driving voltage                                                                                                                         |           |

| 21  | VGH   | С   | Power Supply pin for Positive Gate driving voltage and VSH1                                                                                             |           |

| 22  | VSL   | С   | Negative Source driving voltage                                                                                                                         |           |

| 23  | VGL   | С   | Power Supply pin for Negative Gate driving voltage VCOM and VSL                                                                                         |           |

| 24  | VCOM  | С   | VCOM driving voltage                                                                                                                                    |           |

I = Input Pin, O =Output Pin, I/O = Bi-directional Pin (Input/output), P = Power Pin, C =Capacitor Pin Note 5-1: This pin (CS#) is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled LOW.

- Note 5-2: This pin is (D/C#) Data/Command control pin connecting to the MCU in 4-wire SPI mode. When the pin is pulled HIGH, the data at SDA will be interpreted as data. When the pin is pulled LOW, the data at SDA will be interpreted as command.

- Note 5-3: This pin (RES#) is reset signal input. The Reset is active low.

- Note 5-4: This pin is Busy state output pin. When Busy is High, the operation of chip should not be interrupted, command should not be sent. The chip would put Busy pin High when -Outputting display waveform-Communicating with digital temperature sensor.

Note 5-5: Bus interface selection pin.

| BS1 State | MCU Interface                                          |

|-----------|--------------------------------------------------------|

| L         | 4-lines serial peripheral interface(SPI) - 8 bits SPI  |

| Н         | 3- lines serial peripheral interface(SPI) - 9 bits SPI |

## 6. ELECTRICAL CHARACTERISTICS

## 6.1 ABSOLUTE MAXIMUM RATING

| Parameter                | Symbol | Rating           | Unit |

|--------------------------|--------|------------------|------|

| Logic supply voltage     | VCI    | -0.5 to +6.0     | V    |

| Logic Input voltage      | VIN    | -0.5 to VCI +0.5 | V    |

| Logic Output voltage     | VOUT   | -0.5 to VCI +0.5 | V    |

| Operating Temp range     | TOPR   | 0 to +40         | °C   |

| Storage Temp range       | TSTG   | -25 to+70        | °C   |

| Optimal Storage Temp     | TSTGo  | 23±2             | °C   |

| Optimal Storage Humidity | HSTGo  | 55±10            | %RH  |

Note: Maximum ratings are those values beyond which damages to the device may occur. Functional

operation should be restricted to the limits in the Panel DC Characteristics tables.

9

## 6.2 DC CHARACTERISTICS

The following specifications apply for: VSS=0V, VCI=3.0V, TOPR =25°C.

| Parameter Symbol Condition              |                       | Applicable<br>pin                                           | Min. | Тур.               | Max.  | Unit               |     |

|-----------------------------------------|-----------------------|-------------------------------------------------------------|------|--------------------|-------|--------------------|-----|

| Single ground                           | Vss                   | -                                                           |      | -                  | 0     | -                  | V   |

| Logic supply<br>voltage                 | V <sub>CI</sub>       | -                                                           | VCI  | 2.3                | 3.0   | 3.7                | ~   |

| Core logic voltage                      | V <sub>DD</sub>       |                                                             | VDD  | 1.7                | 1.8   | 1.9                | V   |

| High level input<br>voltage             | VIH                   | -                                                           | -    | 0.8V <sub>CI</sub> | -     | -                  | V   |

| Low level input<br>voltage              | VIL                   | -                                                           | -    | -                  | -     | 0.2V <sub>CI</sub> | V   |

| High level output<br>voltage            | V <sub>он</sub>       | IOH = - 100uA                                               | -    | 0.9V <sub>CI</sub> | -     | -                  | V   |

| Low level output<br>voltage             | V <sub>OL</sub>       | IOL = 100uA                                                 | -    | -                  | -     | 0.1V <sub>CI</sub> | V   |

| Typical power                           | P <sub>TYP</sub>      | V <sub>CI</sub> =3.0V                                       | -    | -                  | 17.4  | -                  | mW  |

| Deep sleep mode                         | PSTPY                 | V <sub>CI</sub> =3.0V                                       | -    | -                  | 0.006 | -                  | mW  |

| Typical operating<br>current            |                       | V <sub>CI</sub> =3.0V                                       | -    | -                  | 5.8   | -                  | mA  |

| Image update time                       | -                     | 25 °C                                                       | -    | -                  | 25    | -                  | sec |

| Sleep mode current Islp_V <sub>CI</sub> |                       | DC/DC off, No clock<br>No input load Ram data<br>retain     | -    | -                  | 25    | -                  | uA  |

| Deep sleep mode<br>current              | ldslp_V <sub>CI</sub> | DC/DC off, No clock<br>No input load Ram data<br>not retain | -    | -                  | 3     | 5                  | uA  |

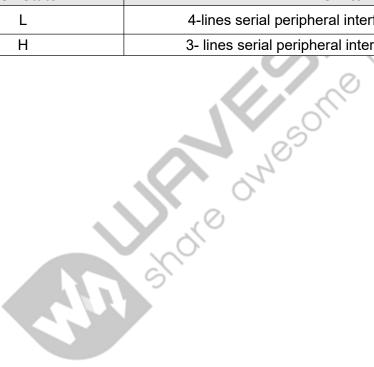

Notes: 1. The typical power is measured with following transition from horizontal 3 scale pattern to

vertical.

2. The deep sleep power is the consumed power when the panel controller is in deep sleep mode.

3. The listed electrical characteristics are only guaranteed under the controller & waveform

provided by Waveshare.

4. Electrical measurement: Multimeter

#### 6.3 AC CHARACTERISTICS

#### 6.3.1 MCU INTERFACE SELECTION

The IC can support 3-wire/4-wire serial peripheral. MCU interface is pin selectable by BS1 shown in Table 6-1.

| Table 6-1 : Interface pins assignment under different MCU interface | Table 6-1 : Interface | pins assignment under | different MCU interface |

|---------------------------------------------------------------------|-----------------------|-----------------------|-------------------------|

|---------------------------------------------------------------------|-----------------------|-----------------------|-------------------------|

|                                                          | Pin Name |      |     |      |     |     |

|----------------------------------------------------------|----------|------|-----|------|-----|-----|

| MCU Interface                                            | BS1      | RES# | CS# | D/C# | SCL | SDA |

| 4-wire serial peripheral<br>interface (SPI)              | L        | RES# | CS# | DC#  | SCL | SDA |

| 3-wire serial peripheral<br>interface (SPI) – 9 bits SPI | н        | RES# | CS# | L    | SCL | SDA |

#### Notes: L is connected to VSS and H is connected to VDDIO.

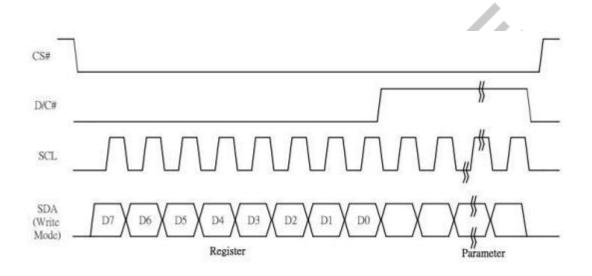

#### 6.3.2 MCU SERIAL INTERFACE (4-WIRE SPI)

The 4-wire SPI consists of serial clock SCL, serial data SDA, D/C# and CS#. The control pins status in 4-wire SPI in writing command/data is shown in Table 6-2 and the write procedure 4-wire SPI is shown in Table 6-2.

| Function      | SCL pin | SDA pin     | D/C# pin | CS# pin |

|---------------|---------|-------------|----------|---------|

| Write command | 1       | Command bit | L        | L       |

| Write data    | 1       | Data bit    | Н        | L       |

#### Table 6-2 : Control pins status of 4-wire SPI

Notes: 1. L is connected to VSS and H is connected to VDDIO.

2. † stands for rising edge of signal.

3. DA (Write Mode) is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0. The level of D/C# should be kept over the whole byte. The data byte in the shift register is written to the Graphic Display Data RAM (RAM)/Data Byte register or command Byte register according to D/C# pin.

Figure 6-1 : Write procedure in 4-wire SPI mode

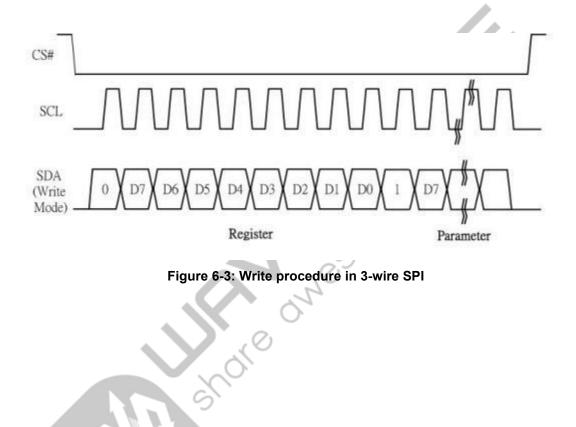

#### 6.3.3 MCU SERIAL PERIPHERAL INTERFACE (3-WIRE SPI)

MCU Serial Peripheral Interface (3-wire SPI) The 3-wire SPI consists of serial clock SCL, serial data SDA and CS#. The operation is similar to 4-wire SPI while D/C# pin is not used and it must be tied to LOW. The control pins status in 3-wire SPI is shown in Table 6-3.

In the write operation, a 9-bit data will be shifted into the shift register on every clock rising edge. The bit shifting sequence is D/C# bit, D7 bit, D6 bit to D0 bit. The first bit is D/C# bit which determines the following byte is command or data. When D/C# bit is 0, the following byte is command. When D/C# bit is 1, the following byte is data. Table 6-3 shows the write procedure in 3-wire SPI.

| Function      | SCL pin | SDA pin     | D/C# pin | CS# pin |

|---------------|---------|-------------|----------|---------|

| Write command | î       | Command bit | Tie LOW  | L       |

| Write data    | Ť       | Data bit    | Tie LOW  | L       |

Table 6-3 : Control pins status of 3-wire SPI

#### Notes: 1. L is connected to VSS and H is connected to VDDIO.

#### 2. † stands for rising edge of signal.

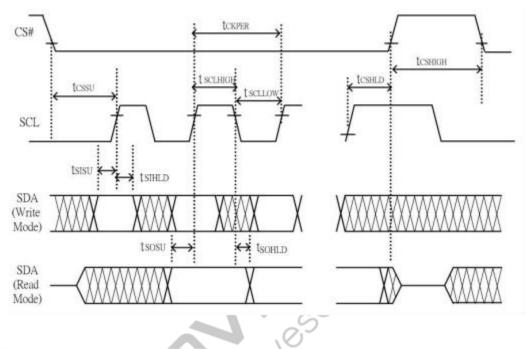

#### 6.4.4 INTERFACE TIMING

#### The following specifications apply for: VSS=0V, VCI=3.0V, TOPR =25°C.

#### Write mode

| Symbol                                                       | Parameter                                                                    | Min | Тур | Max | Unit |

|--------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|-----|------|

| fscl                                                         | SCL frequency (Write Mode)                                                   | -   | -   | 20  | MHz  |

| tcssu                                                        | Time CS# has to be low before the first rising edge of SCLK                  | TBD | -   |     | ns   |

| <b>t</b> CSHLD                                               | Time CS# has to remain low after the last falling edge of SCLK               | TBD |     | -   | ns   |

| tcsnign                                                      | Time CS# has to remain high between two transfers                            | TBD | -   |     | ns   |

| tsclhigh                                                     | Part of the clock period where SCL has to remain high                        | TBD |     |     | ns   |

| tscllow Part of the clock period where SCL has to remain low |                                                                              | TBD | -   |     | ns   |

| tsisu                                                        | Time SI (SDA Write Mode) has to be stable before the next rising edge of SCL | TBD |     |     | ns   |

| tsihld                                                       | Time SI (SDA Write Mode) has to remain stable after the rising edge of SCL   | TBD | -   | -   | ns   |

Read mode

| Symbol   | Parameter                                                                | Min | Тур | Max | Unit |

|----------|--------------------------------------------------------------------------|-----|-----|-----|------|

| fscL     | SCL frequency (Read Mode)                                                |     | -   | 2.5 | MHz  |

| tcssu    | Time CS# has to be low before the first rising edge of SCLK              | TBD |     | 1.0 | ns   |

| tCSHLD   | Time CS# has to remain low after the last falling edge of SCLK           | TBD | -   |     | ns   |

| ссянісян | Time CS# has to remain high between two transfers                        | TBD | -   |     | ns   |

| tsclhigh | Part of the clock period where SCL has to remain high                    | TBD |     |     | ns   |

| tscllow  | Part of the clock period where SCL has to remain low                     | TBD |     |     | ns   |

| lsosu    | Time SO(SDA Read Mode) will be stable before the next rising edge of SCL | TBD | TBD |     | ns   |

| tSOHLD   | Time SO (SDA Read Mode) will remain stable after the falling edge of SCL | TBD | TBD | -   | ns   |

Note: All timings are based on 20% to 80% of VDDIO-VSS

## 7. COMMAND TABLE

|   | man  |    | -              |                |                |                |                |                | _              |                |                       |                                                                                                                                                                                                        |                                                                                                                     |                                                                                                                               |                                                                                          |

|---|------|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|   | D/C# |    | _              | D6             | D5             | D4             | D3             | D2             | D1             | D0             | Command               | Descripti                                                                                                                                                                                              |                                                                                                                     |                                                                                                                               |                                                                                          |

| 0 | 0    | 01 | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              | Driver Output control | Gate setti                                                                                                                                                                                             |                                                                                                                     |                                                                                                                               | N/                                                                                       |

| 0 | 1    |    | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |                       | A[8:0]= 12<br>MUX Gate                                                                                                                                                                                 | 2Bh [POF                                                                                                            | I, 300 MU                                                                                                                     | X<br>(9.01 , 1)                                                                          |

| 0 | 1    |    | 0              | 0              | 0              | 0              | 0              | 0              | 0              | A <sub>8</sub> |                       | WUX Gale                                                                                                                                                                                               | e imes se                                                                                                           | ung as (A                                                                                                                     | [0.0] + 1).                                                                              |

| 0 | 1    |    | 0              | 0              | 0              | 0              | 0              | 0<br>B2        | 0<br>B1        | A8 B0          |                       | B [2:0] = 0<br>Gate scar<br>B[2]: GD<br>Selects th<br>GD=0 [PC<br>G0 is the<br>output sec<br>GD=1,<br>G1 is the<br>output sec<br>B[1]: SM<br>Change si<br>SM=0 [PC<br>G0, G1, G<br>interlaced<br>SM=1, | 000 [POR<br>nning seq<br>e 1st out<br>DR],<br>1st gate o<br>quence is<br>canning o<br>DR],<br>22, G32<br>)<br>64G29 | ].<br>uence and<br>put Gate<br>butput cha<br>G0,G1, G<br>butput cha<br>G1, G0, C<br>brder of ga<br>299 (left ar<br>04, G1, G3 | direction<br>nnel, gate<br>2, G3,<br>nnel, gate<br>33, G2,<br>te driver.<br>nd right gat |

|   |      | 1  |                |                |                |                |                |                |                |                |                       |                                                                                                                                                                                                        |                                                                                                                     | G299 to G                                                                                                                     |                                                                                          |

| 0 | 0    | 03 | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              | Gate Driving voltage  | Set Gate                                                                                                                                                                                               | drivina va                                                                                                          | ltage                                                                                                                         |                                                                                          |

| 0 | 1    |    | 0              | 0              | 0              | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A              | Control               | A[4:0] = 0                                                                                                                                                                                             |                                                                                                                     |                                                                                                                               |                                                                                          |

| • |      |    |                | Ŭ              | Ŭ              | 7.14           | 1.5            | 1.2            |                |                |                       |                                                                                                                                                                                                        | ng from 1                                                                                                           | 0V to 20V                                                                                                                     |                                                                                          |

|   |      |    |                |                |                |                |                |                |                |                |                       | A[4:0]                                                                                                                                                                                                 | VGH                                                                                                                 | A[4:0]                                                                                                                        | VGH                                                                                      |

|   |      |    |                |                |                |                |                |                |                |                |                       | 00h                                                                                                                                                                                                    | 20                                                                                                                  | 0Dh                                                                                                                           | 15                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       | 03h                                                                                                                                                                                                    | 10                                                                                                                  | 0Eh                                                                                                                           | 15.5                                                                                     |

|   |      |    |                |                |                |                |                |                |                |                |                       | 04h                                                                                                                                                                                                    | 10.5                                                                                                                | 0Fh                                                                                                                           | 16                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       | 05h                                                                                                                                                                                                    | 11                                                                                                                  | 10h                                                                                                                           | 16.5                                                                                     |

|   |      |    |                |                |                |                |                |                |                |                |                       | 06h                                                                                                                                                                                                    | 11.5                                                                                                                | 11h                                                                                                                           | 17                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       | 07h                                                                                                                                                                                                    | 12                                                                                                                  | 12h                                                                                                                           | 17.5                                                                                     |

|   |      |    |                |                |                |                |                |                |                |                |                       | 08h                                                                                                                                                                                                    | 12.5                                                                                                                | 13h                                                                                                                           | 18                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       | 07h                                                                                                                                                                                                    | 12                                                                                                                  | 14h                                                                                                                           | 18.5                                                                                     |

|   |      |    |                |                |                |                |                |                |                |                |                       |                                                                                                                                                                                                        |                                                                                                                     |                                                                                                                               |                                                                                          |

|   |      |    |                |                |                |                |                |                |                |                |                       | 08h                                                                                                                                                                                                    | 12.5                                                                                                                | 15h                                                                                                                           | 19                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       |                                                                                                                                                                                                        |                                                                                                                     |                                                                                                                               | 1000000                                                                                  |

|   |      |    |                |                |                |                |                |                |                |                |                       | 08h                                                                                                                                                                                                    | 12.5<br>13                                                                                                          | 15h<br>16h                                                                                                                    | 19                                                                                       |

|   |      |    |                |                |                |                |                |                |                |                |                       | 08h<br>09h                                                                                                                                                                                             | 12.5                                                                                                                | 15h                                                                                                                           | 19<br>19.5                                                                               |

|      | r - 1      | d Tal |                |                |                |                |                | -              | -              | -              |              |            |              |                                                                     |

|------|------------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--------------|------------|--------------|---------------------------------------------------------------------|

|      | D/C#       |       | D7             | D6             | D5             | D4             | D3             | D2             | D1             | DO             | Comm         |            |              | Description                                                         |

| 0    | 0          | 04    | 0              | 0              | 0              | 0              | 0              | 1              | 0              | 0              |              | e Driving  | voltage      | Set Source driving voltage                                          |

| 0    | 1          |       | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Contro       | bl         |              | A[7:0] = 41h [POR], VSH1 at 15V                                     |

| 0    | 1          |       | B <sub>7</sub> | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo             |              |            |              | B [7:0] = A8h [POR], VSH2 at 5V.<br>C[7:0] = 32h [POR], VSL at -15V |

| 0    | 1          |       | C <sub>7</sub> | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | Co             | 1            |            |              | Remark: $VSH1 >= VSH2$                                              |

|      | ] = 1,     |       |                |                |                |                |                |                | 7]/B[7         |                |              |            |              | C[7] = 0,                                                           |

| VSH  | 12 vo      | Itage | setti          | ng fro         | om 2.          | .4V to         | C              |                |                |                |              | e setting  | from 8.8     |                                                                     |

| 3.6  |            |       |                |                |                |                |                | 1000           | 17V            |                |              |            |              |                                                                     |

| 1030 | B[7:0]     |       | VSH2           |                | 8[7:0]         | 100700000000   | /VSH2          |                | A/B[7:0]       | VS             | H1/VSH2      | A/B[7:0]   | VSH1/VSH     |                                                                     |

|      | 8Eh<br>8Fh | -     | 2.4<br>2.5     | 00.0           | Eh<br>.Fh      | 100            | .6<br>.7       |                | 21h<br>23h     |                | 8.8<br>9     | 37h<br>38h | 13<br>13.2   | 0Ah -5<br>0Ch -5.5                                                  |

| _    | 90h        | -     | 2.6            |                | Oh             |                | .8             |                | 24h            | 10             | 9.2          | 39h        | 13.4         | 0Eh -6                                                              |

|      | 91h        | 1     | 2.7            | B              | 1h             |                | .9             |                | 25h            | 20             | 9.4          | 3Ah        | 13.6         | 10h -6.5                                                            |

|      | 92h        |       | 2.8            |                | 2h             |                | 6              |                | 26h            |                | 9.6          | 3Bh        | 13.8         | 12h -7                                                              |

| _    | 93h<br>94h |       | 2.9<br>3       |                | 3h<br>4h       | 10             | .1             | -              | 27h<br>28h     |                | 9.8          | 3Ch<br>3Dh | 14<br>14.2   | 14h -7.5                                                            |

| _    | 94n<br>95h |       | 3<br>3.1       |                | 5h             | 040            | .2             | $\vdash$       | 28h            |                | 10.2         | 3Dn<br>3Eh | 14.2         | 16h8                                                                |

| _    | 96h        |       | 3.2            |                | 6h             |                | .4             |                | 2Ah            |                | 10.4         | 3Fh        | 14.6         | 18h -8.5<br>1Ah -9                                                  |

| _    | 97h        |       | 3.3            | -              | 7h             |                | .5             |                | 2Bh            |                | 10.6         | 40h        | 14.8         | 1Ah -9<br>1Ch -9.5                                                  |

| _    | 98h        |       | 3.4            | -              | 8h             | 1.21           | .6             |                | 2Ch            |                | 10.8         | 41h        | 15           | 161 -5.5<br>1Eh -10                                                 |

| _    | 99h<br>9Ah | -     | 3.5<br>3.6     | -              | 9h<br>Ah       |                | .7             |                | 2Dh<br>2Eh     |                | 11<br>11.2   | 42h<br>43h | 15.2<br>15.4 | 20h -10.5                                                           |

| _    | 9An<br>9Bh | -     | 3.6            | -              | An<br>Bh       |                | .8             | $\vdash$       | 2En<br>2Fh     | _              | 11.2         | 43n<br>44h | 15.4         | 22h -11                                                             |

|      | 9Ch        | -     | 3.8            |                | Ch             |                | 7              |                | 30h            |                | 11.6         | 45h        | 15.8         | 24h -11.5                                                           |

| 1    | 9Dh        |       | 3.9            | В              | Dh             |                | .1             |                | 31h            |                | 11.8         | 46h        | 16           | 26h -12                                                             |

|      | 9Eh        |       | 4              |                | Eh             | 1.22           | .2             |                | 32h            |                | 12           | 47h        | 16.2         | 28h -12.5<br>2Ah -13                                                |

| _    | 9Fh        | -     | 4.1            | -              | Fh             | -              | .3<br>.4       | _              | 33h            |                | 12.2         | 48h        | 16.4         | 2An -13<br>2Ch -13.5                                                |

|      | A0h<br>A1h |       | 1.2<br>1.3     |                | 0h<br>1h       | _              | .4             | -              | 34h<br>35h     |                | 12.4<br>12.6 | 49h<br>4Ah | 16.6<br>16.8 | 2Eh -14                                                             |

|      | A2h        |       | 1.4            |                | 2h             | -              | .6             |                | 36h            |                | 12.8         | 4Bh        | 17           | 30h -14.5                                                           |

|      | A3h        | 4     | 1.5            | C              | 3h             | 7              | .7             |                |                |                |              | Other      | NA           | 32h -15                                                             |

| _    | A4h        | -     | 1.6            |                | 4h             |                | .8             |                |                |                |              |            |              | 34h -15.5                                                           |

|      | A5h<br>A6h | -     | 4.7<br>4.8     |                | 5h<br>6h       |                | .9<br>8        |                |                |                |              |            |              | 36h -16                                                             |

|      | A7h        | -     | +.o<br>1.9     |                | 7h             |                | •<br>.1        |                |                |                |              |            |              | 38h -16.5                                                           |

|      | A8h        |       | 5              |                | 8h             |                | .2             |                |                |                |              |            |              | 3Ah -17<br>Other NA                                                 |

|      | A9h        | 3     | 5.1            | C              | 9h             | 8              | .3             |                |                |                |              |            |              | Ottor IVI                                                           |

| _    | AAh        |       | 5.2            |                | Ah             |                | .4             |                |                |                |              |            |              |                                                                     |

|      | ABh<br>ACh | -     | 5.3<br>5.4     |                | Bh<br>Ch       |                | .5             |                |                |                |              |            |              |                                                                     |

|      | ADh        | -     | 5.5            | -              | ther           |                | IA AL          |                |                |                |              |            |              |                                                                     |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              |                                                                     |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              |                                                                     |

| 0    | 0          | 08    | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 0              |              | Code Set   | ing          | Program Initial Code Setting                                        |

|      |            |       |                |                |                |                |                |                |                |                | OTP P        | rogram     |              |                                                                     |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              | The command required CLKEN=1.                                       |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              | Refer to Register 0x22 for detail.                                  |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              | BUSY pad will output high during operation.                         |

|      |            |       |                |                |                | ,              |                |                |                |                | 0            |            |              |                                                                     |

| 0    | 0          | 09    | 0              | 0              | 0              | 0              | 1              | 0              | 0              | 1              | Write I      | Register f | or Initial   | Write Register for Initial Code Setting                             |

|      |            | 00    | 128            | 100            | 3              | 1000           |                | (9)            | 5              | 200            |              | Setting    | or mud       | Selection                                                           |

| 0    | 1          |       | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |              | county     |              | A[7:0] ~ D[7:0]: Reserved                                           |

| 0    | 1          |       | B <sub>7</sub> | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo             |              |            |              | Details refer to Application Notes of Initia                        |

| 0    | 1          |       | C <sub>7</sub> | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | Co             |              |            |              | Code Setting                                                        |

| 0    | 1          |       | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do             | ]            |            |              | -                                                                   |

|      |            |       |                |                |                |                |                |                |                |                |              |            |              |                                                                     |

| 0    | 0          | 0A    | 0              | 0              | 0              | 0              | 1              | 0              | 1              | 0              | Read         | Register f | or Initial   | Read Register for Initial Code Setting                              |

| 0    |            | UA    | 0              | 0              | 0              |                |                | 0              |                | 0              |              | Setting    | or milial    |                                                                     |

|      |            |       |                |                |                |                |                |                |                |                | 5500         | Soung      |              |                                                                     |

| 3/W# | D/C# | Hex | D7     | D6             | D5                    | D4             | D3             | D2             | D1              | DO | Command            | Description                                                                                                                                            |

|------|------|-----|--------|----------------|-----------------------|----------------|----------------|----------------|-----------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 2 - South tion                                                                                                                                         |

| 0    | 0    | 0C  | 0      | 0              | 0                     | 0              | 1              | 1              | 0               | 0  | Booster Soft start | Booster Enable with Phase 1, Phase 2 and Phase                                                                                                         |

| 0    | 1    | 00  | 1      | A <sub>6</sub> | A <sub>5</sub>        | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub>  | Ao | Control            | for soft start current and duration setting.                                                                                                           |

| 0    | 1    |     | 1      | B <sub>6</sub> | B <sub>5</sub>        | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B1              | Bo |                    | A[7:0] -> Soft start setting for Phase1                                                                                                                |

| 1000 |      |     | 1000 A |                | and the second second |                |                |                | COMPANY AND ANY |    | -                  | = 8Bh [POR]                                                                                                                                            |

| 0    | 1    |     | 1      | C <sub>6</sub> |                       | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub>  |    | -                  | B[7:0] -> Soft start setting for Phase2<br>= 9Ch [POR]                                                                                                 |

| 0    | 1    |     | 0      | 0              | D <sub>5</sub>        | D4             | D <sub>3</sub> | D2             | D1              | Do |                    | C[7:0] -> Soft start setting for Phase3<br>= 96h [POR]<br>D[7:0] -> Duration setting<br>= 0Fh [POR]                                                    |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | Bit Description of each byte:<br>A[6:0] / B[6:0] / C[6:0]:                                                                                             |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | Bit[6:4] Driving Strength<br>Selection                                                                                                                 |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 000 1(Weakest)                                                                                                                                         |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 001 2                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 010 3                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 011 4                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 100 5                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 101 6                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 110 7                                                                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 111 8(Strongest)                                                                                                                                       |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | Bit[3:0] Min Off Time Setting of GDR<br>[ Time unit ]                                                                                                  |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 0000                                                                                                                                                   |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | ~ NA<br>0011                                                                                                                                           |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 0100 2.6                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 0101 3.2                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 0110 3.9                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 0111 4.6                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1000 5.4                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1001 6.3                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1010 7.3                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1011 8.4                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1100 9.8                                                                                                                                               |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1101 11.5                                                                                                                                              |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1110 13.8                                                                                                                                              |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 1111 16.5                                                                                                                                              |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | D[5:0]: duration setting of phase<br>D[5:4]: duration setting of phase 3<br>D[3:2]: duration setting of phase 2<br>D[1:0]: duration setting of phase 1 |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | Bit[1:0] Duration of Phase<br>[Approximation]                                                                                                          |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 00 10ms                                                                                                                                                |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 01 20ms                                                                                                                                                |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 10 30ms                                                                                                                                                |

|      |      |     |        |                |                       |                |                |                |                 |    |                    | 11 40ms                                                                                                                                                |

|      | man  |                 | ble |    |    |        |    |         |                |                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------|-----------------|-----|----|----|--------|----|---------|----------------|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W# | D/C# | Hex             | D7  | D6 | D5 | D4     | D3 | D2      | D1             | D0             | Command                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      |      |                 |     |    |    |        |    |         |                |                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0    | 0    | 10              | 0   | 0  | 0  | 1      | 0  | 0       | 0              | 0              | Deep Sleep mode         | Deep Sleep mode Control:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0    | 1    | · · · · · · · · | 0   | 0  | 0  | 0      | 0  | 0       | A <sub>1</sub> | A <sub>0</sub> |                         | A[1:0]: Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |      |                 |     |    |    |        |    |         |                |                |                         | 00 Normal Mode [POR]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |      |                 |     |    |    |        |    |         |                |                |                         | 01 Enter Deep Sleep Mode 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |      |                 |     |    |    |        |    |         |                |                |                         | 11 Enter Deep Sleep Mode 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |      |                 |     |    |    |        |    |         |                |                |                         | After this command initiated, the chip will<br>enter Deep Sleep Mode, BUSY pad will<br>keep output high.<br>Remark:<br>To Exit Deep Sleep mode, User required to<br>send HWRESET to the driver                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0    | 0    |                 | 0   | 0  | 0  |        | 0  | 0       | 0              |                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0    | 0    | 11              | 0   | 0  | 0  | 1<br>0 | 0  | 0<br>A2 | 0<br>A1        | 1<br>A0        | Data Entry mode setting | Define data entry sequence<br>A[2:0] = 011 [POR]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |      |                 |     |    |    |        |    |         |                |                |                         | A [1:0] = ID[1:0]<br>Address automatic increment / decrement<br>setting<br>The setting of incrementing or<br>decrementing of the address counter can<br>be made independently in each upper and<br>lower bit of the address.<br>00 –Y decrement, X decrement,<br>01 –Y decrement, X decrement,<br>10 –Y increment, X decrement,<br>11 –Y increment, X increment [POR]<br>A[2] = AM<br>Set the direction in which the address<br>counter is updated automatically after data<br>are written to the RAM.<br>AM= 0, the address counter is updated in<br>the X direction. [POR]<br>AM = 1, the address counter is updated in<br>the Y direction. |

| 0    | 0    | 12              | 0   | 0  | 0  | 1      | 0  | 0       | 1              | 0              | SW RESET                | It resets the commands and parameters to<br>their S/W Reset default values except<br>R10h-Deep Sleep Mode<br>During operation, BUSY pad will output<br>high.<br>Note: RAM are unaffected by this<br>command.                                                                                                                                                                                                                                                                                                                                                                                                                                  |